C-MOS ANALOG-SW "4066"傪巊偭偨斈梡DBM偺帋嶌

巐敿悽婭慜偺1980擭崰丄C-MOS僨僶僀僗偱傾僫儘僌僗僀僢僠偺4066傪巊梡偟偰Corwin宆偺曄暅挷婍傪嶌偭偨帠偑偁傞丅HF僕僃僱僇僶偺庴怣婡傪惢嶌拞偵丄傆偲儈僉僒乕偲偟偰巊偊傞偺偱偼偲巚偭偨丅堦斒偺僟僀僆乕僪4屄傪巊梡偟偨儕儞僌曄暅挷婍偱偼丄僟僀僆乕僪偵RF偲LO怣崋傪壛偊LO怣崋偺惓晧偱僟僀僆乕僪傪愗懼偊偰丄RF怣崋偺棳傟傞曽岦惈傪僗僀僢僠偡傞傕偺偱偁傞丅偟偨偑偭偰僟僀僆乕僪偺愗懼摿惈偼LO怣崋偺乽攇宍偲儗儀儖乿偵埶懚偡傞丅傑偨RF偲LO偑僟僀僆乕僪撪偱崿嵼偡傞偨傔丄愗懼埲奜偺崿崌偑峴傢傟傞壜擻惈偑偁傝丄梋傝婥帩偪椙偔側偄丅偦偙偱LO怣崋傪僎乕僩惂屼怣崋偲偟偰埖偭偨傾僫儘僌僗僀僢僠傊偺婜懸偑傢偄偰棃偨丅LO怣崋傪嬮宍攇偵曄姺偟偰僗僀僢僠傪惂屼偡傞偨傔丄媫弒側愗懼偑壜擻偱丄傑偨RF偲LO偺捈愙愙怗偼側偔側傞丅

(1)峔丂惉

(1)峔丂惉

擖椡僩儔儞僗偼FB-801(#43嵽)偵僩儕僼傽僀儔(L1/L2/L3)偱5夞姫偔丅L1偼撈棫偝偣擖椡僐僀儖偲偟丄L2/L3偼僩乕僥儉億乕儖偵愙懕偟丄愙懕揰傪婎弨偵惓晧偺RF怣崋傪傾僫儘僌僗僀僢僠偵摫偔丅偙

偙偱偼傾僫儘僌僗僀僢僠偼2宯摑偲偡傞偑丄捠夁儘僗傪掅尭偡傞堊偵2屄暲楍愙懕偟偰偄傞丅弌椡懁偼暲楍愙懕偟IF弌椡偲偡傞丅LO擖椡偼Ex-RO僎乕僩74HC86傪巊梡偟丄偦偺摿挜傪惗偐偟偰愗傝懼偊僞僀儈儞僌偺堦抳偟偐偮埵憡斀揮偟偨惓丒晧弌椡傪摼傞丅僀儞僶乕僞偱娙扨偵斀揮偡傞曽朄傕偁傞偑丄偙偺応崌偼僀儞僶乕僞乕屌桳偺抶墑帪娫偑偦偺傑傑愗傝懼偊帪娫偺抶傟偲側傞偺偱僴僀僼儗偱偼岲傑偟偔側偄丅惓丒晧弌椡偵傛傝傾僫儘僌僗僀僢僠74HC4066偺僎乕僩傪嬱摦偡傞丅

揹尮偼74HC僔儕乕僘偺応崌偼6V傑偱曐忈偝傟偰偄傞偑丄TTL偲偺屳姺傪峫椂偟5V偲偟偨丅

僩儔儞僗偲74HC4066/74HC864偼儐僯僶乕僒儖婎斅偵慻傒傾儖儈僟僀僉儍僗僩働乕僗偵廂傔傞丅RF/LO/IF億乕僩偼BNC僐僱僋僞偱擖弌椡偡傞丅揹尮偼DC僕儍僢僋傛傝嫙媼偡傞丅揹尮儖乕僩偵偼僶僀僷僗傗LFP夞楬傪愝偗奜晹偲崅廃攇揑側愨墢傪峴偆丅

(2)惢丂嶌

(2)惢丂嶌

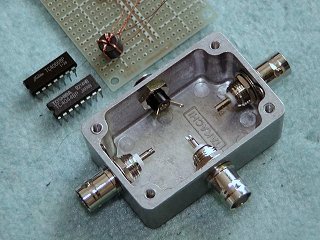

幨恀忋偼FB-801偵僩儕僼傽僀儔偱姫偄偨僩儔儞僗丅慄嵽偼0.26mmUEW(億儕僂儗僞儞慄)丅嵍偼5夞姫偒偱塃偼4夞姫偒丅嵟掅廃攇悢偵僀儞僟僋僞儞僗偑塭嬁偡傞偺偱丄栚揑廃攇悢偵崌傢偣偨姫偒悢偑昁梫偱偁傞丅

幨恀壓偼TAKACH偺傾儖儈僟僀僉儍僗僩働乕僗TD-6-3-N傪壛岺偟BNC僐僱僋僞3屄偲DC僕儍僢僋1屄傪庢傝晅偗偨條巕丅DC僕儍僢僋偼LO億乕僩偺斀懳懁偵庢傝晅偗偨偑丄LO億乕僩偲摨堦曽岦偵偟偨曽偑婎斅偺弌偟擖傟偑梕堈丅

夞楬恾拞偺壜曄掞峈婍偼丄RF擖椡偑IF偵楻傟崬傓検傪嵟彫偵挷惍偡傞VR丅夞楬忋偵敪惗偡傞僗僩儗乕梕検偺塭嬁偑偁傝丄峀懷堟側摿惈傪摼傞偺偼側偐側偐擄偟偄丅

LO擖椡偵姫悢斾1:3偺揱憲慄楬僩儔儞僗傪憓擖偟僗僥僢僾傾僢僾傪恾傝丄擖椡SWR偑壓偑傞傛偆偵50x3x3=450兌偱廔抂偟偰偄傞丅偙偙偱偼揹椡偼慡偔昁梫側偄偺偱揹尮揹埑憡摉埲忋偵僗僥僢僾傾僢僾偟僗僀僢僠儞僌偵昁梫側儗儀儖傪壱偖丅

IC傪慻傒崬傫偩婎斅偼棤岦偒偵幚憰偝傟偰偄傞丅婎斅忋偺攝慄偼幚憰慜偵嵪傑偣丄幚憰屻僩儔儞僗摍偺攝慄傪峴偆丅側偍偙偺Ver偵偼僶儔儞僗挷惍偼柍偄丅憡庤偼崅廃攇側偺偱傾乕僗夞楬偱嫟捠僀儞僺乕僟儞僗傪帩偨側偄傛偆偵攝慄偡傞丅

(3)敪揥宍

(3)敪揥宍

4066偵偼尦乆4屄偺傾僫儘僌SW慺巕偑撪憼偝傟偰偄傞丅偙傟傪僟僀僆乕僪偺儕儞僌曄暅挷婡偺傛偆偵愙懕偟偨儈僉僒傪峫偊偰傒傞丅

恾偼僟僀僆乕僪4屄傪傾僫儘僌SW偵抲偒姺偊偨條巕偱偁傞丅僪儔僀僽偼Ex-OR僎乕僩偵傛傞嬱摦夞楬偱偁傞丅僟僀僆乕僪曽幃偺傛偆偵丄僗僀僢僠儞僌宱楬偲怣崋宱楬偑廳忯偟側偄偺偱夞楬傕僔儞僾儖偱丄摿偵僩儔儞僗偵偼僙儞僞乕僞僢僾偼昁梫偲偟側偄丅

暯峵搙偼傾僫儘僌僗僀僢僠偺僆儞掞峈偵埶懚偡傞偺偱僶儔僣僉偺柍偄僨僶僀僗傪慖戰偡傞偐丄旝挷惍梡偺VR傗R(SW偵捈楍)傪昁梫偲偡傞丅僆儞掞峈偼嫙媼偡傞揹埑傗廃曈偺壏搙偵傕埶懚偡傞偺偱丄偦偺塭嬁偑暯峵搙偵偳偺掱搙塭嬁傪梌偊傞偐傪攃埇偡傞昁梫偑偁傞丅

埨掕偼偦偙偦偙偱僠儍儞僺僆儞僨乕僞傪慱偆応崌偲丄暯峵搙偼棊偪傞偑埨掕搙傪慱偆応崌偲偱嶌傝曽偑曄傢偭偰偔傞丅

擖弌椡僩儔儞僗偼1:1:1偺僩儕僼傽僀儔偱姫偒丄姫偒悢斾1:2偺僩儔儞僗傪嶌傟偽Z斾偼1:4偱僗僀僢僠懁偼50x4=200兌偺夞楬偑峔惉偱偒傞丅SW慺巕偺僆儞掞峈傪50兌掱搙偵尒崬傔偽2屄偱100兌偲側傝200/100+200=2/3=67%掱搙偺儗儀儖偱(懠偺儘僗偼柍帇)偱峔惉弌棃傞丅姫偒悢斾傪1:3偵偟偰Z斾傪1:9偵偡傟偽峏偵儗儀儖掅壓偼梷偊傜傟傞偑丄崱搙偼廃攇悢摿惈偑栤戣偵側偭偰偔傞丅

(4)傑偲傔

摉弶4066偐傜DC僆僼僙僢僩偑弌傞偐偲巚偄IF弌椡懁偵DC僽儘僢僋梡偺僙儔儈僢僋僐儞僨儞僒傪憓擖偟偰偄偨偑丄僥僗僞偱恾傞偲慡偔僆僼僙僢僩偼柍偄偨傔徣棯偟偨丅傑偨IF億乕僩偺廔抂掞峈傕揚嫀偟偰昁梫嵟彫尷偺峔惉偲偟偨丅

DBM偺摿挜偲偟偰慺捠傝怣崋偺梷埑偑偁傞丅偡側傢偪RF傗LO億乕僩偐傜擖椡偝傟偨怣崋偑IF億乕僩偵弌偰棃側偄偺偑儀僗僩偱偁傞偑丄嶌傝偭曻偟偱偼拞乆偦偆偼側傜側偄丅尰忬偱偺梷埑検傪應掕偡傞偲栺-40dB掱搙偱偁傞丅偪側傒偵Minicircuits幮偺ADE-1偼RF億乕僩偑-53dB丄LO億乕僩偑-60dB(at3MHz)偱偁傞丅

Ex-OR僎乕僩偺巊梡偱惓丒晧偺愗傝懼偊偑椙岲偵峴傢傟偰偄傞偑丄僨儏乕僥傿斾偑50%偵側偭偰偄側偄丅側偤側傜LO擖椡惓尫攇傪扨弮偵74HC僎乕僩偱庴偗偰偄傞偐傜偱偁傞丅杮棃側傜僐儞僷儗乕僞摍偵傛傝僨儏乕僥傿斾50%偺嬮宍攇偵偟偨偄偲偙傠偱偁傞丅

傑偨僗僀僢僠僨僶僀僗傪2屄暲楍偵偟偰僆儞掞峈偺掅壓傪慱偭偰偄傞偑丄尦乆堦掕偺掞峈抣傪帩偭偰偄傞偨傔捠夁儘僗偑敪惗偟偰偄傞丅Minicircuts幮偺ADE-1偵斾傋3dB掱搙懡偄丅僩儔儞僗偺姫慄偼1:1:1偩偑丄2師懁傪峏偵崅偄僀儞僺乕僟儞僗偵愝掕偟偰僆儞掞峈偺塭嬁傪夞旔偡傞庤傕偁傞丅偙偺応崌偼IF懁偵僗僥僢僾僟僂儞僩儔儞僗偑昁梫偵側傞丅

C-MOS僨僶僀僗偱峔惉偝傟偰偄傞偨傔偲悇應偝傟傞偑丄揹尮傪愗偭偰傕儈僉僔儞僌摦嶌偑峴傢傟廃攇悢曄姺偝傟嫽枴傪堷偔丅偙傟偼揹尮儔僀儞偲GND娫偵掞峈傪憓擖偟曻揹儖乕僩傪嶌傞帠偱夝寛偡傞丅傑偨僪儔僀僽僎乕僩偱偁傞EX-OR傪74LS86摍偺TTL偵曄峏偡傟偽偙偺尰徾偼柍偔側傞傕偺偲巚傢傟傞丅

(5)嶲峫ゥsolation應掕

庤尦偵偁傞DBM偺Isolation傪應掕偟偰傒偨丅應掕偼RF億乕僩偐傜IF億乕僩丄媦傃LO億乕僩偐傜IF億乕僩偵楻傟弌偡儗儀儖偵偮偄偰偺傒應掕偟偨乮柍擖椡億乕僩偼50兌偱廔抂)丅

(5)嶲峫ゥsolation應掕

庤尦偵偁傞DBM偺Isolation傪應掕偟偰傒偨丅應掕偼RF億乕僩偐傜IF億乕僩丄媦傃LO億乕僩偐傜IF億乕僩偵楻傟弌偡儗儀儖偵偮偄偰偺傒應掕偟偨乮柍擖椡億乕僩偼50兌偱廔抂)丅

僒儞僾儖偼Minicircuits偺ADE-1丄TDK偺CB3034M丄偦傟偵帺嶌偺74HC4066DMB偱丄應掕偼栺3MHz偱+7dBm偺CW傪RF偲LO億乕僩偵拲擖偟IF億乕僩傪僗儁傾僫偱娤應偟偨丅拲擖廃攇悢傪栺3MHz偲偟偨棟桼偼丄偙偺廃攇悢傪LO偲偟偰3.5MHz懷傪IF=455KHz偵曄姺偟偰暦偄偰偄傞偐傜偦偺傑傑棳梡偟偨偩偗丅

昞偵寢壥傪傑偲傔偨丅傾僀僜儗乕僔儑儞偵偮偄偰偺傒偱尒傞側傜丄帺嶌偺74HC4066DBM偼丄捠夁儘僗暘傪嵎偟堷偄偰傕僩僢僾偺惉愌偱偁傞丅扐偟峀懷堟偵偳傟偩偗懳墳偟偰偄傞偐偼枹應掕丅