はじめに

JA1VKV田中氏よりCalogic社のDMOS SWITCHデバイス"SD8901HD"を使った受信機"SD8901HD_RECEIVER"の完成を告げるメールが届いた。

2006年8月、BBSの読者へ共同購入を募り、このデバイスを田中氏のマネージメントで購入した事を昨日の事のように思い出している。

写真の様に、田中氏は同じ受信機を2台製作された模様でその情熱に驚かされる。そして内部を拝見すると、シールドボックス処理を前提とした丁寧な作りに強いポリシーと夢を感じる。

この写真を眺めながら、自分のジェネカバ受信機の進捗状況のアバウトさを反省する日々が暫く続いている・・・何とかしなければ。

田中氏からは「7MHz専用でIF=8.83MHzのシングルコンバ−ションでウェ−ブ電子のDDSをリファレンスにしてPLLを組んでいる。SD8901HDは局発レベルが25dBm程度必要なのでその辺のスプリアス対策が大変だった。」とコメントを頂戴しております。

SD8901を3rdIPを40dB付近で使おうとしたら20dBm(100mW)程度の局発が必要かと想像していたが、田中氏はなんと25dBmも注入されていて驚いた。25dBmと言ったら316mWにも達するからもはやQRP-Txではないか!。

以下田中氏から頂戴した写真をご紹介します。

内部のユニット構成

内部のユニット構成

左は上からBPF-RF-AMP、MIX-POST-AMP、POST-FILTER、SSB/CW-FILTER、IF-AMP、DET-AF-AMP。

下は左からBPF-16MHz/BPF-8MHz、LPF-3MHz、PLL-UNIT/DDS-UNIT。

局発PLL出力とケースに収めたSD8901HD_RECEIVER

局発PLL出力とケースに収めたSD8901HD_RECEIVER

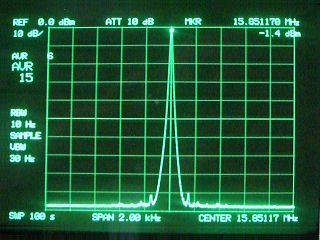

左は局発出力20dBmの出力を示しているが、近傍スプリアスは-90dB以下を示している。

下はケースに収めたSD8901HD_RECEIVER。メインダイアルの左にPRE-AMP制御、左下にAF-GAINとIF-FILTER-SEL、左上にS-METERとAGC-SPEED、右下にAF-FILTER-SELとAGC-CONTにRF-GAIN、右上にDDS-VFO制御が配置されている。