Nov 23. 2005 D/A変換10KHz桁の連続性を探る

同僚のN氏から4桁表示可能なデジタルテスターを借用してきた。1V桁を表示していても1mVまで測定が出来るもの(METEX社M-3850)で、どうやら秋葉原の秋月電子で購入したものらしい。これによりD/A変換10KHz桁の連続性を確認してみた。グラフは500KHzから2.5MHzの2MHzスパンを10KHzステップで測定したものを表している。図から分かる様に全体としては1次関数で推移しているが桁上げ時に周期的にグリッチがあって、上下方向が乱れている部分が確認できる。なお測定は1mVオーダーで比較的高いZを相手にしているので外来のノイズ等には注意を払いう。Audioで言うならマイクロフォンレベルなので、取り扱いはシールド線などを使用して行わないと正しいデータが取得できない。

全周波数帯でデータ取得するのは膨大な時間が掛かるため2.5MHzまでとした。ちなみに32MHzで1.12V。初期設定はDDS-VFOを50MHzで出力した際にD/A出力が約50mVになるようにOFFSETを設定してある。

なお今回からD/A出力は反転出力表示としている。

D/A変換1KHz桁の連続性と1KHz桁ラダーD/A出力

更に1KHz桁の連続性を確認した。図は500KHz~520KHzの状態を示したもので、左がD/A変換最終出力である。10MHz桁に比べたら1/10000の加算比だからどんなものかと思っていたが、かなりアバウトと言うよりとんでもない出力になっている。グラフはスムージング処理をしていないので三角が際立って見える。とてもD/Aと呼べるシロモノではない。ちなみに右は1KHzD/AのバッファOPアンプ出力を見たものであるが非常に素直で問題は無い…注意:方向性は反転している。と言うことで混合比の関係でレベル的に見てS/Nの劣化による誤動作が考えられる。したがって加算器の抵抗器を全体に低い方向にシフトさせ、1KHz桁でも10KHz桁並のレベルで取り扱う方が好ましい。だだこの比率だと、10MHz桁の加算抵抗は10ΩとなりOPアンプから見るとオーバーロード(最大数字9で1.83V)になったり、内部抵抗との関係で誤差が増えるので簡単には踏み切れない。いずれにせよ基板上のS/Nや電源ラインのリップルやS/Nを現在より数倍~10倍程度改善する必要がある。

加算抵抗値変更でD/A変換1KHz~10KHz桁の連続性改善

1KHz桁の動作を安定にするためにS/N改善を行う。加算器の抵抗値を約半分に下方シフトし、動作レベルを上げる。基板上は高くない周波数とは言え、立ち上がりの急峻なパルスを扱っているのでアナログ的に見たら基本的にノイズの巣。抵抗値は1KHz:1M→470K、10KHz:100K→47K、100KHz:10K→4.7K、1MHz:1K→470、10MHz:100→47とし、配線もIC間を直接結んだ。また帰還抵抗も1K→470に変更。回路図も変更した。

これにより1KHz桁の加算器入力S/Nが向上し左図の様に1KHz桁D/A出力で諧調がはっきり見えるようになった。上のグラフに比べると劇的な改善である。この抵抗値はOPアンプの許容損失や内部抵抗との関係もあり余り下げる訳には行かないので注意する。ここでは47Ω/0.5W(1%)を使用した。

1KHz桁の動作を安定にするためにS/N改善を行う。加算器の抵抗値を約半分に下方シフトし、動作レベルを上げる。基板上は高くない周波数とは言え、立ち上がりの急峻なパルスを扱っているのでアナログ的に見たら基本的にノイズの巣。抵抗値は1KHz:1M→470K、10KHz:100K→47K、100KHz:10K→4.7K、1MHz:1K→470、10MHz:100→47とし、配線もIC間を直接結んだ。また帰還抵抗も1K→470に変更。回路図も変更した。

これにより1KHz桁の加算器入力S/Nが向上し左図の様に1KHz桁D/A出力で諧調がはっきり見えるようになった。上のグラフに比べると劇的な改善である。この抵抗値はOPアンプの許容損失や内部抵抗との関係もあり余り下げる訳には行かないので注意する。ここでは47Ω/0.5W(1%)を使用した。

下図は1KHzステップで500~600KHzを変化させた時のD/A変換出力。加算抵抗以外は触っていないが妙なグリッチや上下関係が反転するような状況は確認出来ない。ただ10KHzへの桁上がり時に同じ値がつながる傾向があるのでオフセットの調整が必要である。しかし無調整でこの特性だからまずまずの成績と言えるだろう。1mV単位の電圧を観測するので測定器の分解能やf特・周辺ノイズも加味され面白い…理解してやらないととんでもないデータになる。グラフの縦軸はあくまでも目安で、波形の傾向を見ている事に注意して頂きたい。

Nov 21. 2005 COFFEE BREAK…松下電器周波数直線VC

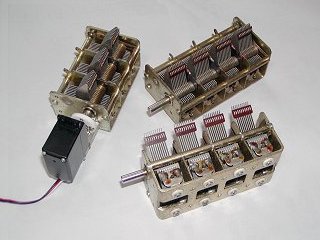

松下電器が1960年代に製造販売していた周波数直線VCをご存知だろうか?。VCの背面には「MODEL ECV-3DX18 CAP 11-198PF」と記されている。これは3連だが、4連の場合はECV-4DX-18となる。これ以外に230PFのECV-4DC-230やスプレッド用18PFのECV-4RC-02の周波数直線群、それに一般用途430PFの容量直線型がラインナップされていた。

写真はECV-3DX18(RC-SERVO付き)とECV-4DX18(2個)。1973年頃に静岡の岩崎ラジオから多量に購入したものの一つ。後者は最近友人のJA2INO/水谷氏から譲り受けたもの。

ECV-*DX18はfmax/fmini=2.35を守るとその間が周波数直線になる。オーナーがこのVCの存在を知ったのは1967年の「初歩のラジオ」10月号の製作記事である。当時中学1年生でこの記事をそっくり真似た受信機をその2年後に製作しSWL/BCLを楽しんでいた。それ以降高1中2受信機はもとより、RFのプリセレクタはこの周波数直線VCのお世話になってきた。あの430PFのVCに満足できなかった少年には最高の贈り物だった。

それにしても水谷氏も物持ちが良い。一つはボロボロの箱に半分顔を出し未使用だった。もう一つは線材がハンダ付けされていたが綺麗に払った。プリセレクタには4連を使用する予定で、複同調回路をRFアンプの前後に配し、結合度を低くして高Qを維持し、利得は0dBに近い状態で使用する。

Nov 20. 2005 D/A変換ボードその他追加修正

D/A変換ボードで以下の追加作業を行った。

①Anti No Letter制御をを100KHz桁にも追加

VFOダイアルを回して誤って100KHz桁が無くなるとBCDに「1111」が出力されるため、サーボがとんでもない位置に飛ぶのを避けるため。

②VFOのWD/RD制御ボタンを押した時にSERVO回路を停止させる回路追加

WD/RD制御ボタンを押すと1Hz桁以外の桁は無表示になるため、1Hz桁以外全ての桁「1111」のBCDコードが出力される。全ての桁の状態を見るのは大変なので、1HKz桁が「1111」になった時のみAND処理を行いインバーター経由で最終出力に挿入したアナログSWを制御する。SERVO制御回路は無心号になった場合今までの状態を機械的に保持する性質がある。

③下位桁の桁上がり直線性の改善

これは検討課題だが、下位桁例えば1KH⇔10KHz⇔100KHzと桁上がり・下がりする時に連続性にバラツキがある。1KHzステップでVFOダイアルを回すと、100KHzステップでは感じなかったバックラッシュがSERVOで発生する。各桁の状況を掴んでから対応するが、現在良質なmV計がないため正確な作業が出来ないでいる。

写真は実験的にRC-SERVOを駆動している様子。VFO周波数データをLEDディスプレイから横取りし、7Segment信号から各桁データをBCD変換し、更にD/A変換して得たDC電圧でSERVO駆動回路のPWMを制御している。

Nov 19. 2005 D/A変換出力のリップル対策

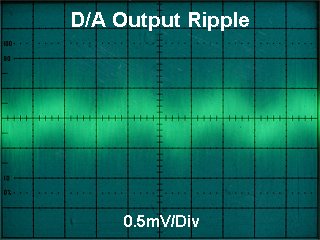

D/A変換出力にリップルが残っているためRC-SERVOに接続した時にハンチングを生じていた。D/A変換時のラッチタイミングの関係とその対策の為にデータの1/8周期を0レベルでクランプしているからだ。デジタルレベルでの対策は基板上に空きスペースが無いため既に限界に達している。

そこで加算器や最終バッファアンプの帰還抵抗にCを抱かすなどの対策を試みたがRC-SERVOがゴリゴリ言っている。Cの容量を増加すると改善の方向ではあるが、今度はタイムラグが大きくなり追従性が悪くなる。このためバッファアンプを本格的なButterworth型のLPFに変身させ対策を試みた。扱うのはDCなのでカットオフ周波数は1Hz以下の超低周波にしている。あまり低くするとRC-SERVOの追従時間に影響するので、ダイアルノブを回して程よく追従する範囲に設定する。

左図は加算器とLPF部を書き出したもの。これだけの回路で劇的な改善が得られリップルは1mVp-p以下に収まった(今までは10mVp-p)。

なおこのテストに併せ、当該OPアンプの電源を±駆動に変更した。シングル電源だとオフセットをキャンセルする作業が大変なのと、オフセットを含んだ計算が面倒だからである。

D/A変換ボードがいよいよ形になってきたが、最終的なインターフェイス電圧を考えなければいけない。RC-SERVO側が負方向なので、出力はそれに合わすが可変レンジはどれ位が適当だろうか。本当なら32~0.5Vが分かり易いがそんな電源は使っていないし危ない。3.2~0.05Vと言う手もあるが…悩ましい。

写真は上図の定数でD/A出力を測定したもの。オシロをACカップルのフルゲインにして0.5mV/Divで表示している。1mVp-p位に見えるが、高い周波数成分が乗っているのでリップルは0.5mVp-p程度と思われる。これによりRC-SERVOとの接続テストで良好に動作しハンチングは無くなった。

なお参考だが、この程度のレベルになると電源ラインに重畳しているノイズやリップルと同程度か或いはそれ以下である。直流は電気回路の基本であるが、交流から完全な直流を得る事は本当に難しいと思う。こうしたデータを見るとバッテリがいかに良質な直流電源かが分かる。余談だがバッテリによる直流電源を用意し置くとハムやノイズ対策に便利である。

作業中にVFOダイアルをステップを変えて回してみたが、やはり下位桁でもデータ飛びがあって、桁上げや桁下がりがある時にD/A出力の連続性が失われる場合がある。各桁のオフセット調整が必要になる。現在は10Mz桁は入念な合わせを行い727KΩでBIASをかけているが、1MHz~1KHz桁は暫定的に在り物の680KΩで実施している。

D/A変換ボードの作業を終わろうとしても、新しいテーマが次から次へ出てきて中々簡単に終わらせてくれない。日々修行と言った感が強い。デバイス規格表以外の技術資料などを紐解かなくても、何となく対策や措置が出来てしまうのは長年の経験だろうか・・・。

Nov 18. 2005 D/A変換OPアンプバッファのオフセット調査

10MHz桁D/A変換OPアンプのオフセットを調査した。1MΩの高抵抗を5V(Reg)ラインから供給することで、10MHz桁が表示された時に落ち込むレベルを補正していたが未だ若干低目であった。そこで抵抗値を下げどのような変化をするか確認してみた。図は手持ちの関係で680KΩ(赤)に変更したものと、1MΩ(青)のままの状態を比較している。青は10MHzのポイントで若干落ち込んでいたが、赤は大分改善された。しかし僅かではあるが持ち上がり過ぎた感がある。したがって750KΩ前後に最適値があると思われる。この辺りの高抵抗は余り使わないので、CRボックスをかき回してやってお探し当てた物。

なおNov17でA/D出力のリップルが気になったため、加算OPアンプLPFのCを330μと膨大な値に変更しテストしている。

Nov 17. 2005 D/A変換出力でRC-SERVOを駆動してみた

早る気持ちを抑えきれずD/A変換出力でRC-SERVO(VC)を駆動してみた。以前実験したRC-SERVOの制御電圧は2.75~3V程度なので、D/A変換出力をVRで利得とオフセット調整しレベルシフトする。ところがここで新発見。RC-SERVO基板の制御電圧方向とD/A変換ボード出力のポラリティが逆で、周波数を上げるとVCが左回り(容量増方向)する事が判明。このためRC-SERVO基板への接続は加算OPアンプ出力から取る事にした。写真はこの様子で、VFOダイアルを回すとSERVOが動きVCが回りだす。まだ定量的な特性や直線性などを見るまで環境が整わないが、SERVOのモーターとギアが音を立てVCを回す姿に思わず手を叩きたくなる心境である。電気で動くも物ってやっぱり面白い。ここで幾つか課題が発覚したのでまとめておく。

①D/A変換出力DCにリップル(10mVp-p)がありRC-SERVOがハンチング

②RC-SERVO制御入力がかなりHi-Zなの静電的カブリでも影響を受ける

③VCの回転角度180度のリミットを考慮する必要がある

ということでD/Aに若干の手直しや見直しが必要になった。またバンド情報検知やウィンドウコンパレータ等によるリミット制御など、RC-SERVOへ安定な制御電圧を供給する回路が必要になってくる。久々にVCが登場し受信機を作っている雰囲気になった。D/A変換もRC-SERVO駆動も制御に対する出力は1次関数で成立しているので、周波数直線VCの動作条件を守ればDCの管理のみでVFOに連動したプリセレクションが実現すると目論んでいる。

Nov 15. 2005 D/A変換の直線性改善

D/A変換の直線性を改善した。10MHz桁が現れる時とそれ以下の桁との整合性が悪かったがバッファOPアンプに微量のBIASを与えることで解決した。しかし係数(傾き)が揃わず10MHzへ桁上がりする部分で折れ線になっていた。

実験中に500KHz付近に周波数を変更すると出力電圧が落ち着くまでに時間の掛かるのを確認。可笑しい?。調べると加算OPアンプ出力は正常で、最終の反転バッファOPアンプが時定数を持っている事が分かった。

それでLPF用に帰還抵抗にパラっていた10μタンタルコンを撤去すると反応が早くなった。更にBIAS設定をレンジをギリギリまで広げてみた。もしやと思い測定したのが左の青グラフ(赤グラフは昨日のデータ)。大幅に特性が改善され、全体に渡って直線で推移している。このレンジで見れば間違いなく1次関数グラフと言えそうだが、1KHzステップなど部分拡大したらどうなるかは別途調査する。

この出力電圧をバンドごとにレベルシフトしてRCサーボを駆動すれば、表示周波数に応じたRF同調が実現する。RFバンドが一つの場合は良いが、計画では6バンド(0.5-1/1-2/2-4/4-8/8-16/16-32)であるから、D/A変換出力電圧に応じて各バンドを選択する検知と駆動回路が必要になる。これも楽しい作業になりそうだ。

Nov 14. 2005 D/A変換の直線性改善方法

10MHz桁に数字が入る瞬間のつなぎにギザ(三角)が出来ている件の対策を検討した。その後のカーブは直線で推移しているので、10MHz桁D/AバッファのOPアンプにオフセットを与えるようにした。このバッファは100%帰還の正転アンプなので、出力とマイナス入力が直付けされている。BIASを与えるのはプラス側でしか出来ない。そこで5V電源から高抵抗(とりあえず1MΩ)を介しプラス側に接続してみた。これにより10.000MHzと9.999MHzの変換出力が同じになった(今までは0.1V程度あった)。

グラフはこの状態で入出力特性を取ったものでギザ部分が無くなっている。ただしこの状態では9.999MHzから10.000MHzへのステップな無いので、高抵抗はもう少し小さくする必要がある。また10MHz未満で傾きの変化が残っており調整の必要がある。

左図は加算器OPアンプに少量のBIASを与え出力オフセットを改善した回路。前述の如く5Vラインから1MΩを経由しているが、この状態で9.999MHzと10.000MHzが同じ値を出力するので、抵抗値は1MΩより若干少なめでも良い。この値はカット&トライで決定する予定。曲線の夫々の傾きから見て、最適値は900KΩ前後であろうか…。この値は電源電圧の一寸した変動により影響を受けるので、電源周りの安定化は必須である。何故0.1V程度のオフセットが発生するかは考察の余地がある。

なお併記してあるPullUp抵抗は、手抜きのDiodeANDの動作をより完全にするためのもの。これがないと波形のな鈍りやBit間の落ち込みが見られ、アナログSW(4066)の動作が不安定になる可能性がある。この処理でアナログSWの制御入力の波形は、シュミットトリガのCMOSバッファを1段通した位に綺麗な波形になる。

久しく触れていなかったが、ラダーD/Aの抵抗R=10KΩ。したがって2R=20KΩ。比較的高い値だが、CMOSを使って駆動し、結果的にアナログSWで短絡(ON抵抗との比率、CMOSから見た負荷状況)するなどの処理を考えるとまぁ程々の選択だったかなぁと考えている。

また精度1%級の抵抗をラフに組み合わせたD/Aでもかなり精度が望めることが分かり大きな収穫と言える。

Nov 13. 2005 無表示(No Letter)のD/Aミュート回路・・・無調整の「Frequency-Voltage特性」

DDS-VFOのLED表示は1MHz運用では10MHz桁、100KH運用では1MHz以上の桁に何も表示されない。LEDの7Segmentが全てOFFの状態なのだが、74C915にこの状態が入力されるとBCD出力に「1111」を出力してしまう。この値はフルビットなのでBCDで扱う0~9までの数字よりはるかに大きな値を出力してしまう。74C915の特性で止むを得ないのだが、運用上は非常に厄介で何らかの方法で取り去る必要がある。無表示桁を「0」表示すれば対応できそうだが、見た目は悪いし、PIC側のプログラム修正が必要になる。

そこで以前より記述していたが、BCDの「1111」状態をAND処理で拾い上げ、アナログSWをゲートする事にした。そこで問題になるのはアナログSWを何処に入れるかである。当初はラダーD/Aの直後のOPアンプバッファとに間にカスケードで入れ、信号のON/OFFを試みたが、OPアンプ側が非常にHi-ZのためアナログSWの動作がクリチカルになり不採用。次にOPアンプの入力を接地する方法をテストしたところ良好なミュートがかかった。

図は最終的な回路である。AND回路は本来なら4入力のゲートICを使うべきだろうが、スペースの関係でDiodeのみで構成している。特にプルアップはしていないが問題なく動作している。DiodeはBCDのどれか一つでも「0」になると4066をオープン状態にするが、全て「1」になるとショート状態になり信号をミュートする。

無調整の状態でどの程度の「周波数-電圧特性」があるか測定してみた。グラフは0.5~32MHz間を0.5MHzステップでプロットしたものである。下方から1MHzになる時は気付かなかったが、下方から10MHzになる時に大きなギザが入っている。赤線は最初に測定したもので、青線はOPアンプのオフセットを若干調整したもの。赤線は全体にたるんだ感じの特性になっているが、青線は改善されギザ部分を除けばほぼ1次関数で推移している。なお特性は、加算器の混合比はもとよりOPアンプの電源やオフセットそれに直線性も絡んでいると思われる。OPアンプについては最適なBIASを与え動作範囲を直線範囲に置く必要がある。ギザは1MHz桁以下と10MHz桁の混合比が考えられる。

無表示対策で信号を接地するやや強引な手法でミュート動作をさせており、完全なゲート回路ではないのでやや心配な向きもあるが、青線の如くギザ以外はまずまずの特性である。ギザについては良質なゲート機能つきのバッファアンプがあれば改善が容易だと思われるが…何処かにあるだろうか。何しろ基板上にはもうスペースが無い。

こうした細工は受信機作りとは無縁と思われる方もいらっしゃると思うが、目的に併せて論理回路を組み結果をもたらす過程で多くのノウハウを残してくれ、総合的な技術レベルの向上につながっている。とにかくやっていて楽しくなる。VFOダイアルを回すと連動してD/A変換ボードのDC出力が変わり、テスターやオシロスコープの表示が変わっていく。まるで時計仕掛けの様である。

Nov 12. 2005 74C915のラッチを復活…下隣桁データ混入対策

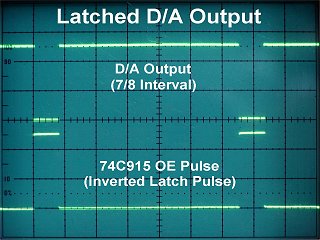

D/A変換出力が8桁インターバルの1桁時間(1.6mS)しか出力しないのは余りにも不便なため、再び74C915のラッチ回路を生かした。過去に述べたように、この場合1.6ms幅で下隣桁データが誤出力されてしまう。1インターバルの1/8程度だから良いかぁ?なんて考えていたが、D/A出力を測定するとやっぱり値が可笑しくなり対策が必要な事が分かるる。

色々と対策方法を考えたが、波形観測中に誤出力タイミングはラッチ制御パルスと同じタイミングであることが判り、そのタイミングで74C915の出力制御OEをゲートする事にした。74C915のOE入力の論理方向はラッチ入力とは逆であるため、ラッチパルスを反転させているIC0の入力側から取る事にした。

この作業により誤出力はミュートされ、1インターバルの7/8間出力を確保することが出来た。現実的には基板上スペースの問題があって、D-FF等の部品増加は出来ず、IC変更と大移動を行って処理している。またIC0インバータには今まで6個入り4584(14P)を使用していたが、8個入り74HC240(20P)に変更し、余った部分は無表示時のデータ制御に使用する等のスペース確保を行っている。

写真はラッチパルスの反転パルス(下)で誤出力部分をミューとしたD/A出力(上)の波形。この作業に合わせ回路を大幅変更した。写真をクリックすると見る事が出来る。なお今までの回路はそのまま残している。

Nov 10. 2005 もう一つの表示無し桁処理について…PICプログラムの修正完了で数字"7"データOK

数百KHzオーダーの表示の場合は10MHzと1MHz桁の表示が無くなる。この時7SegmentコードをBCDに変換すると「1111」となりフルビットをD/Aしてしまう。この件についての対策は既に述べている。

実はこれ以外に数字表示が無くなる動作がこのDDS-VFOにはある。メモリデータを読み書きするWDとRD動作の時である。これらは1Hz桁にメモリ番号を表示するが他の桁は全て無表示になる。この状態を真面目にD/A変換するととんでもない値が出力されるので、あらかじめサーボ動作を停止(状態維持)するための信号を出力する必要がある。この検知には今までの手法と同様にBCD出力でANDをとって行うが、全ての桁でANDをとるのは大変で無意味なので基板上で処理している1KH又は10KHzの桁のみで行う事にする。

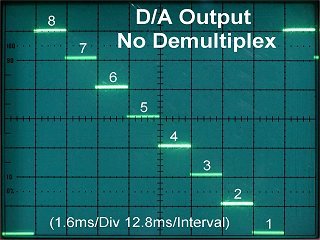

なお本日、数字"7"のプログラム変更をウェーブ電子へ依頼していたPICが届いた。簡単な変更だったため少額有償で受け付けて頂いた。自分でプログラムが書ければ良いのだが、未だそこまで技術力が無いので今回はウェーブ電子様様である。写真は早速実装してテストした様子である。LEDディスプレイに「12.345678MHz」と表示させた時のD/A変換出力である。ただしIC0/4584は抜き、Demultiplex動作は停止させて撮影している。この波形で見る限りではレベル方向においてD/Aは非常に良好に動作をしている。

ここまで来ると後は既に記述している無表示時の処理とD/Aデータのラッチ処理が出来ればこのD/A変換ボードでの作業は終了する。

Nov 6. 2005 表示無し桁の処理方法…フロントパネルのノブを変えてみたら

LEDの数字表示が「無」の場合、DDS-VFOは7Segmentデータに全セグ「L」レベルを出力する。この場合74C915のBCD出力は「1111」を出力する。したがって表示が無い桁ではフルビットが出力され、D/A変換器も最大電圧を出力する。BCDは2進化10進数なので0~9までの表現、すなわち「0000」~「1001」しか扱わないのだが、表示「無」のために74C915はこうした特殊コードを含ませているようだ。これの問題を解決するには、BCDに「1111」が出ないように74C915をプログラム出来れば良いのだが無理な相談なので、BCD出力を「1111」でAND処理しD/A出力をゲートすれば良い(回路図暫定修正)。

口で言うのは簡単だが実際には色々問題がある。一つはD/A変換ボード上にICを載せるスペースが殆ど無いこと。それにD/A出力は直接加算器につながっているので、ゲートデバイスの通過抵抗が問題になってくる。前者はICやその他部品の再配置で逃げるしかないが大作業だ。後者はデジタルレベルでゲートすれば楽だがこれもICスペースが無く中々悩ましい。

本日清水無線(清水区浜田町)を十数年振りに尋ね業務機器用のノブを購入してきた。写真は早速入れ替えて様子を見ているところ。つまむ部分の直径は今までの物とほぼ同じだが、ツバが付き内側に凹みがあるので軸受けのナットが程よく隠れ使い易い。雰囲気も悪くなく2重ノブにも対応出来るが、ちょっと重たいだろうか?…さてどうしたものか。

COFFEE BREAK…SS-1Rの解説"HamJournal/No.7"の思い出

7360を受信機ミキサ管として使用した米Squires Sanders社の受信機SS-1Rの事が気になり、実家にHamJournal/No.7を持ちに帰った。No.7は昭和51年(1976年)7月10日発行だから、既に29年の歳月が流れている。SS-1Rの構想の発表は1963年頃(QST)だから、今から数えると42年も前の事になる。この号にはJA1AEA鈴木OMが「Squires Sanders, Inc のSS-1R 真空管式受信機の挽歌」と題してP31~P41(一部P149)で克明に紹介されている。読み物としても資料としても非常に貴重なものである。冒頭で鈴木OMは…十余年ほどまえにビーム切り替え管7360が開発され、この真空管を使って実用化された唯一のアマチュア無線用受信機…と紹介し、更に…混変調、相互変調などの受信障害については、最近になってようやく注目されてきたものだが、SS-1Rではビーム変換管と高周波増幅部なしというとり合わせで、この様な問題について十年も以前から現今の高級受信機より以上の性能を引き出していた…と続けている。

オーナーはこの号を東京出張中に購入し帰路の東名高速バスでむさぼり読んだ。当時局発を殺してもガサゴソ言う相互変調に悩み、冗談に家庭用の5球スーパー(日立エーダS-540)の局発を殺したら非常に静かな事に驚きを覚え、高1中2を作るなら高1は利得0dBでイメージ比のみを稼ぎ、中2は中3にすべきと言う結論を持っていた。この記事はその考えに非常に近かったため大いに感化され、受信機を製作するときの良きバイブルとなった。写真は久し振りに紐解いたHamJournal/No.7のP31。

Nov 5. 2005 フロントパネルに汎用プッシュ型SWを追加する

しばらくデジタルICを突っつく時間が経過したが、本日久し振りにフロントパネルの機械工作を行った。良い気分転換になる。

写真の如くAudio-JackとATT-SWの間に、ATTと同種のSW(MIYAMA/DS-801)で白色の物を取り付けた。パネルには暫定的に「CAL」とレタリングしてみたが、まだ気分でやっているので、最終的に「Audio」は「HeadPhones」になるが、2個のプッシュSWはどうなるかは未定。

この丸型プッシュSW最大の特徴は、パネルの加工が容易と言う事に尽きる。16mmΦのシャシパンチで打ち抜き、リーマで若干のサイズ合わせを行い、穴の下方に回転防止キリカキを入れるだけである。四角穴だとSWとの合わせ作業に時間が掛かり、複数になると並びににも常に注意を払う必要があり面倒だ。しかし、丸穴だとそうした心配が全く無く、センターポンチ打ちの精度のみに注意すれば良い。

なおキリカキを穴の下方に入れるのは、誤ってキリカキを大きくしてしまった時に、上から覗いてもそのミスを見え難くするための配慮(工夫)である。

このプッシュSWはメイク接点1回路とLEDが内蔵されている。回路構成にもよるが、押した時にLEDを点灯するためには被制御回路との連携が必要になる。また当初は緑色SWを電源用に考えていたが、パネルスペースを有効活用するためにAF-GAINをSW付きVRにして、これを当てる考えでいる。

COFFEE BREAK…部屋の掃除とフロントパネル&と基板類の記念撮影

休日で散らかっていたゴミを整理した。吸い込みが悪かった掃除機ので中を覗いてみたら袋にゴミが詰まり石の如くパンパン状態。袋を取り出したが予備袋が無いため、パンパンの袋からゴミを摘み出す事になった。そしたら出てくるは出てくる、袋にはここ数年間のゴミの歴史が全て詰まっていた。日記もここまでは正確に書けないぞ。その時何をやっていたかが分かるって言うもの。例えば前回の単身赴任で住んでいた川崎市多摩区のアパートの畳のイグサとか、その時に誤って吸ってしまったタイラップ等など…。ゴミでも懐かしく思えるので不思議である。

写真は掃除後に工作中の受信機のフロントパネルとDDS-VFO(右上)とD/A変換ボード(左上)を並べ、通電した状態を記念撮影したもの。色々と考えるとパネルのノブ数がどんどん増えていくので、あるところで割り切る必要がある。例えばRFゲインなんて本当に必要なの?…先輩のJA2DJH石黒氏がその様なメールを投げて来た。その昔SSBの復調にはRFゲインを調整してBFOレベルと合わせる芸当が必要だったが、今はIF帯域制限が良好で目的外信号も問題ないレベルまで抑圧できるから、AGCは掛けっぱなしでフルゲインも殆ど問題はない。氏の言われる通りで、むしろ時定数のFAST/SLOWの切り替えと入力ATTの併用が使い易いと考えている。写真のノブは気に入っているのだが、軸受けナットを隠す凹みがスカート部に無いのでややパネル間に隙間が残る。ひょっとしたらこいつも交換するかも知れない。

Nov 4. 2005 "7"のデコードミスの原因

74C915の入力に数字"7"のデータが入力された時に、D/A変換出力が「0V」になる件について調査した。

JA2XCR/丸尾氏から送って貰ったナショセミ社のマニュアルとにらめっこをしていると、妙な事に気付きワンポーズあってから「これだ!」と飛び上がった。それは分かってしまえば何て事は無い話だ。

図左に示すようにDDS-VFOからの7Segmentデータのフォーマットは「abcf」がHで「deg」がLである。ところが74C915では"7"のフォーマットは「abc」がHで「defg」がLとなっている。すなわち「f」部分の取り扱いに違いがあり、数字"7"が正常にでコードできなかったのである。

74C915に図左の入力があるとBCD出力はHi-Zとなり電圧出力は無いので結果としてD/A変換は「0V」を出力していた。

この解決策はハード的には図左のセグメントデータをデコードして「f」データラインをUnenableするか、ソフト的にはDDS-VFOのプログラム書き換えがある。現実的にはハードで対策する方が簡単だが、ICを乗せるスペースが殆どなくなってしまった。さてどうするか・・・。

そんな所で時間を費やしているのなら、最初からPLDでロジックを書いた方が修正が楽で良いのに!・・・と丸尾氏の声が聞こえて来そうである。

「f」セグメントを数字"7"で使うか否かは規格上どうなっているのだろうか・・・。

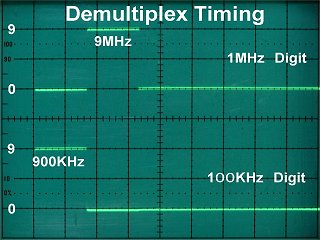

Nov 3. 2005 D/A変換ボードDemultiplexタイミング対策と"7"のデコードミス

久し振りの休日で再びA/D変換ボードを検討する。多重データをタイミングよくストローブ出来ず、下桁データが1クロック分顔を出す現象が続いていた。ICマニュアルをひっくり返して見ていたら不具合に気が付いた。データラッチしている74HC175は最終出力がD-FFだ!。オリジナルLEDボードは、この多重データにタイミングを合わすようにLEDのストローブを行っているが、Latch等の遅延素子は使用していない。しかし74C915にはノーマルLatch-FFが1段挿入されている。したがって、そのままではタイミングが合わないのでストローブ用デコーダ74HC238の出力を1クロックずらして対策したつもりでいた。ところが前述の74HC175のD-FFに対し74C915はノーマルLatch-FFなのでトリガタイミングが合わない模様。

そこで何とか多重データとストローブのタイミングを合わすために・・・

①74C915をLatchスルーにして、出力OE(OutputEnable)をストローブする

②これに併せてストローブ用デコーダ74HC238の取り出しをオリジナルLEDボードと同じにする

この作業で正常動作が期待できるかもしれない・・・。早速回路図の如く修正し動作確認するとズバリOKになった。ところがLatch無しなので、出力は1クロック分で、多重したタイミングの位置でしか出力しない。また新しい課題だ。何とか74C915内蔵のLatchを有効に使いたい。このLatchがD-FFなら一挙に解決なのだが・・・。写真は*9.9*****MHzを表示させた場合。

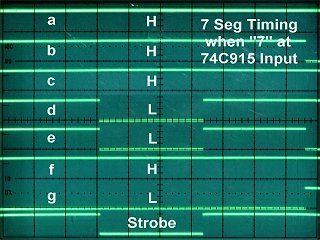

数字"7"のデータが入力した時に、74C915のBCD出力が「0111」にならなければいけないところが「0000」になり、D/A出力が「0V」になってしまう現象について調査を行った。

数字"7"のデータが入力した時に、74C915のBCD出力が「0111」にならなければいけないところが「0000」になり、D/A出力が「0V」になってしまう現象について調査を行った。

気の利いた多現象オシロスコープが無いので、2現象オシロスコープをEXT同期にして74C915に入力する7Segmentデータのタイミングを夫々測定した。それらの波形をデジカメで撮影しPC上で合成してみたみたのがこの写真。

NS社のマニュアルによれば、74C915は7Segmentの「a・b・c・f」がHighの時にBCD出力が「0111」になる事になっている。写真を見ると分かるがStrobeしている期間の7Segmentデータは「a・b・c・f」がHighで入力データとしては問題ない。ではどうしてこの時のBCD出力が「0000」になってしまうのだろうか?。

74C915が壊れていると思い別の物と入れ替えてみても状況は変わらない。或いは74C915の使い方に間違いがあるのだろうか?。ひょっとしたらIC自身がロット不良で全て同じ様に壊れているのだろうか?。眠れない夜が続きそうである。

それにしてもオシロスコープの能力不足を補うため、デジカメにストレージしてPCで合成するなんて涙ぐましいと思う。最近記憶力が落ちてHだったかLだったかの話が怪しくなるので、こうして写真にしておくと覚えになって良い。

中々高周波の話が始まらないが頭の中では構想が煮詰まってきた。